Welche Komponenten hat ein Computer?

- CPU

- ALU

- Register File

- Programm Counter

- Memmory Accessser

- DMEM

- IMEM

- Controller

- Memory

- IO (Datenbusse)

-

Hard Drives

-

GPU

- Display

-

Network

-

Sound

-

Keyborad

-

Mouse

-

Design Goals

Computer Architecture Desing Goals

Link to original

Moor’s Law

Moore‘s Law

Moore sagte selber: „We‘re approaching the size of atoms which is a fundamental barrier […]. We have another 10 to 20 years before we reach a fundamental limit.[…]“ (2005)

Aber: Kein Naturgesetz, sondern eine Prognose dessen, was ökonomisch sinnvoll ist.

Timeline

- Gordon Moore (1929 — 2023), Mitbegriinder von Intel

- Stellt Prognose auf:

1968: Verdopplung der Transistordichte alle 12 Monate

1975: Korrektur auf 24 Monate

Ende von Moore’s Law

Link to original

Unterschied zwischen Architektur und Mikroarchitektur?

- Architektur

- Spezifikationen die alles deffinieren um Programme für das System zu schreiben.

- Enthalten das Instruction Set

- Microarchitekutr

-

Der logische Aufbau des Systems

-

Eine spezifische Implementierung des Systems

-

Beispiel für eine Architektur? Warum RISCV?

ARM

RISC V

x86

M4 (System on a Chip)

Unterschied zwischen D Latch und D Flip Flop?

SR Latch

Link to original

D Latch

Two inputs:

- CLK: controls when the output changes

- D (the data input): controls what the output changes to

Link to original

- samples on the falling edge

Latch vs Flip-Flop (samples on the rising edge)

D Flip-Flop

Function:

- Samples D on rising edge of CLK

- When CLK rises from 0 to 1, D passes through to Q

- Otherwise, Q holds its previous value

- Q changes only on rising edge of CLK

⇒ Called edge-triggered

vs D Latch (samples on the falling edge) Latch vs Flip-Flop

siehe auch

Flip-Flop with Enable

Link to original

Flip-Flop with Reset

Latch vs Flip-Flop

Link to original

Wofür braucht man eine Clock?

Clock

Link to original

- Clock is a general mechanism that triggers transition from one state to another in a sequential circuit

- Clock synchronizes state changes across many sequential circuit elements

- Combinational logic evaluates for the length of the clock cycle

- Clock cycle should be chosen to accommodate maximum combinational circuit delay

Von-Neumann-Architektur? Shortcomings? Systembus

Das von-Neumann Prinzip

Voll-elektrischer Rechner

Binäre Darstellung der Daten

Benutzung einer arithmetischen Einheit

Benutzung eines Steuerwerkes

Interner Daten- und Programmspeicher

Prinzipieller Aufbau eines Rechners

Link to original

Was ist ein Multiplexer (n:1)? Gibt es mehrere Outputs?

Multiplexer

Link to original

Demultiplexer 1:n, Decoder n:n

Decoders

Link to original

Instruction gegeben, zeigen welcher Instructiontyp? Wo ist rd, rs1, rs2?

RISC V Instruction Format

RISC V R-Type

Link to original

RISC V I-Type

RISC V S-Type

RISC V B-Type

RISC V U-Type

RISC V J-Type

Unterschied zwischen Bitshift, rotieren nach rechts?

Logical Shifters

Binary Shifters using Logic Gates - 101 Computing

Link to original

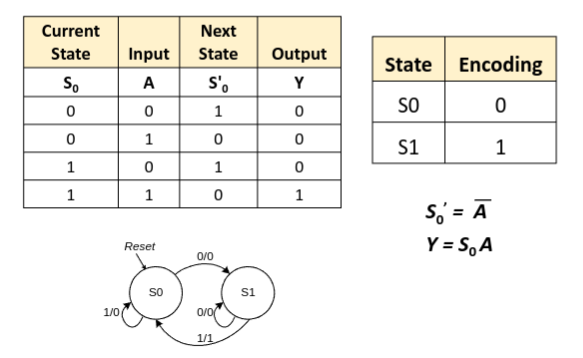

FSM

Moore FSM

Link to original

Mealy FSM

Link to original

Beispiel Datapath, wie macht man ab einem gewissen Punkt weiter? Ist das Jump oder nicht? Wie viele Zyklen? Einen, weil Single Cycle Processor

Transclude of RISC-V-Impelmentation.excalidraw

Was macht Register Zero?

⇒ Immer 0

⇒ Kann nicht beschrieben werden

RISC V Register Set

Link to original

Pipelining, was passiert da? Wie viele Zyklen pro Instruction?

Weniger als ein Cycle bei der Ausführung einer Instruction mit Pipelining

Es gibt bis zu 5 Stufen in der Ausführung eines RISC V Befehles.

Jeder Clock Cycle kann ein neuer Befehel in der ersten Stufen gestartet werden.

Pro Clock Cycle bewgen sich die Befehle eine Stufe weiter

“Pipelined” RISC-V Datapath

Link to original

Pipeline Register brauchen, welcher Teil der Pipleline welcher Teil der Instruktion beinhaltet.

RISC V Controller

RISC V Controller

Link to original

Pipelining. die drei Hazards

Structural hazard

Hardware does not support access across multiple instructions in the same cycle.

Can not access Memory in two stages

⇒ Separate IMEM, DMEM Memories

Data hazards

Daten sind noch werden erst von vorigem Befehl gelanden und stehen noch nicht zu Verfügung.

Control Hazards

bedingter sprung kann dazu führen das der Befehl danach garnicht ausgeführt wird.

Wie werden Sachen kompiliert von C zu Executable?

Was passiert beim Linken? Linker Patches, S. 37

Memory Mapping, also das konzept bei dem die peripheriegeräte wie Speicher behandelt werden .

Als Beispiel wird ein Gerät gegeben. Welche Adresse schreiben, auf welcher wird gelesen?

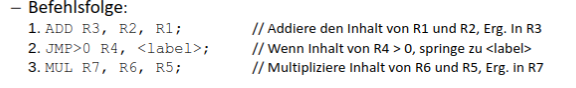

Data Flow Graph

Link to original